第6课

约 354 个字 22 张图片 预计阅读时间 1 分钟

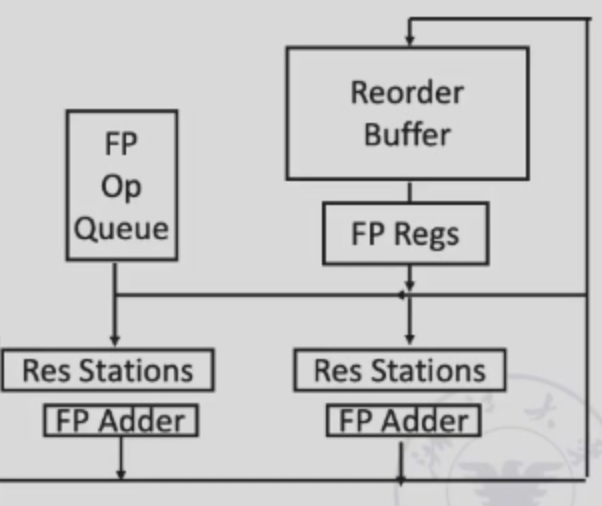

Hardware-Based Speculation¶

1. 主要结构¶

- 之前是直接写到结果寄存器(FP Regs),而现在是先到ROB中;

2. 指令阶段¶

- Issure:从FP Op Queue中获取指令;

- Execution:对操作数进行操作(EX);

- Write result:结束执行(WB),把所有的结果写到ROB去;

- Commit:更新结果寄存器;

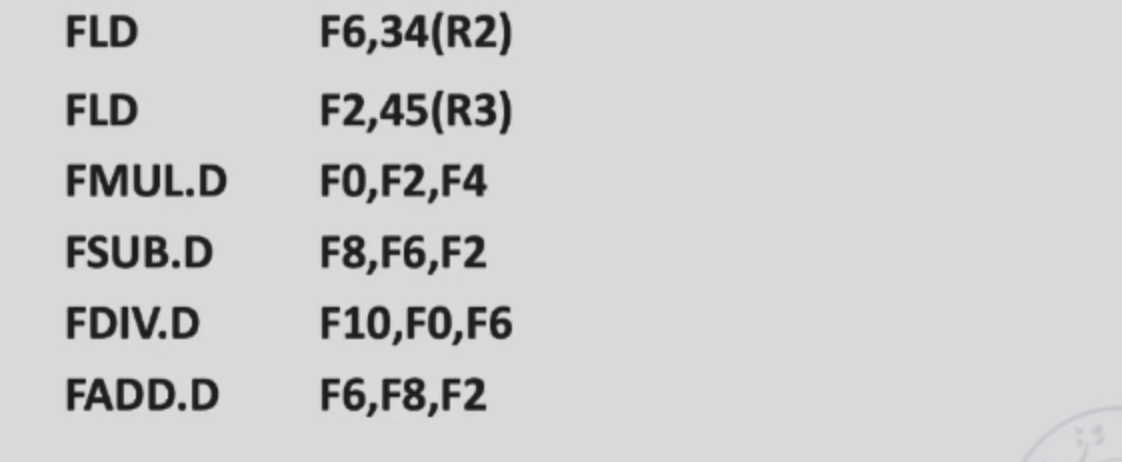

3. 一个例子¶

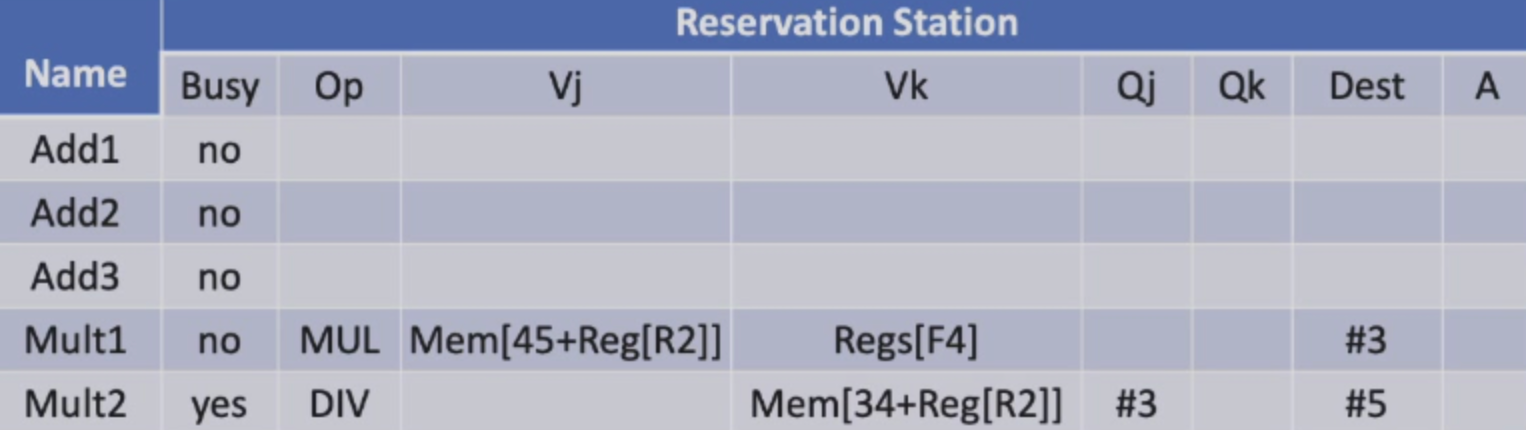

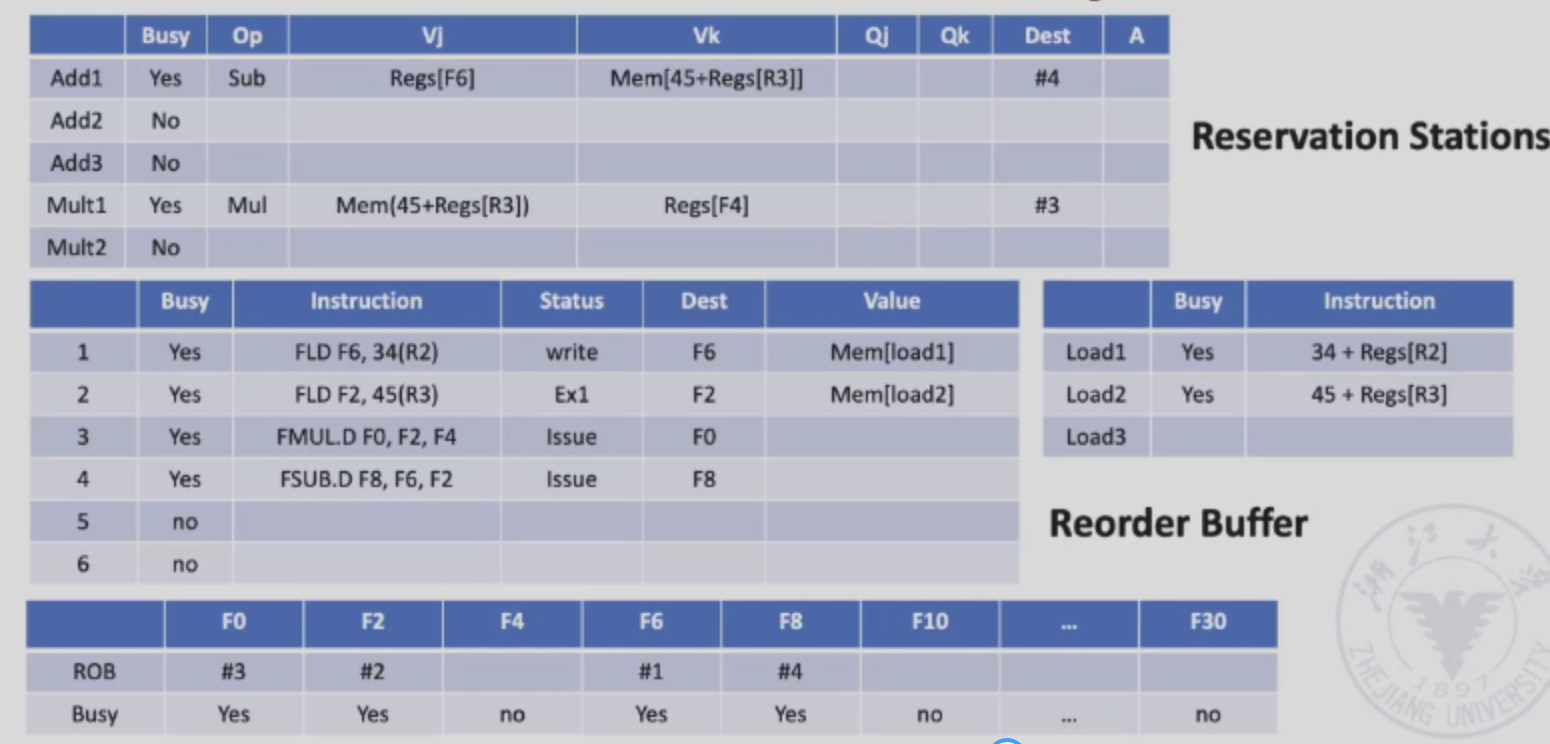

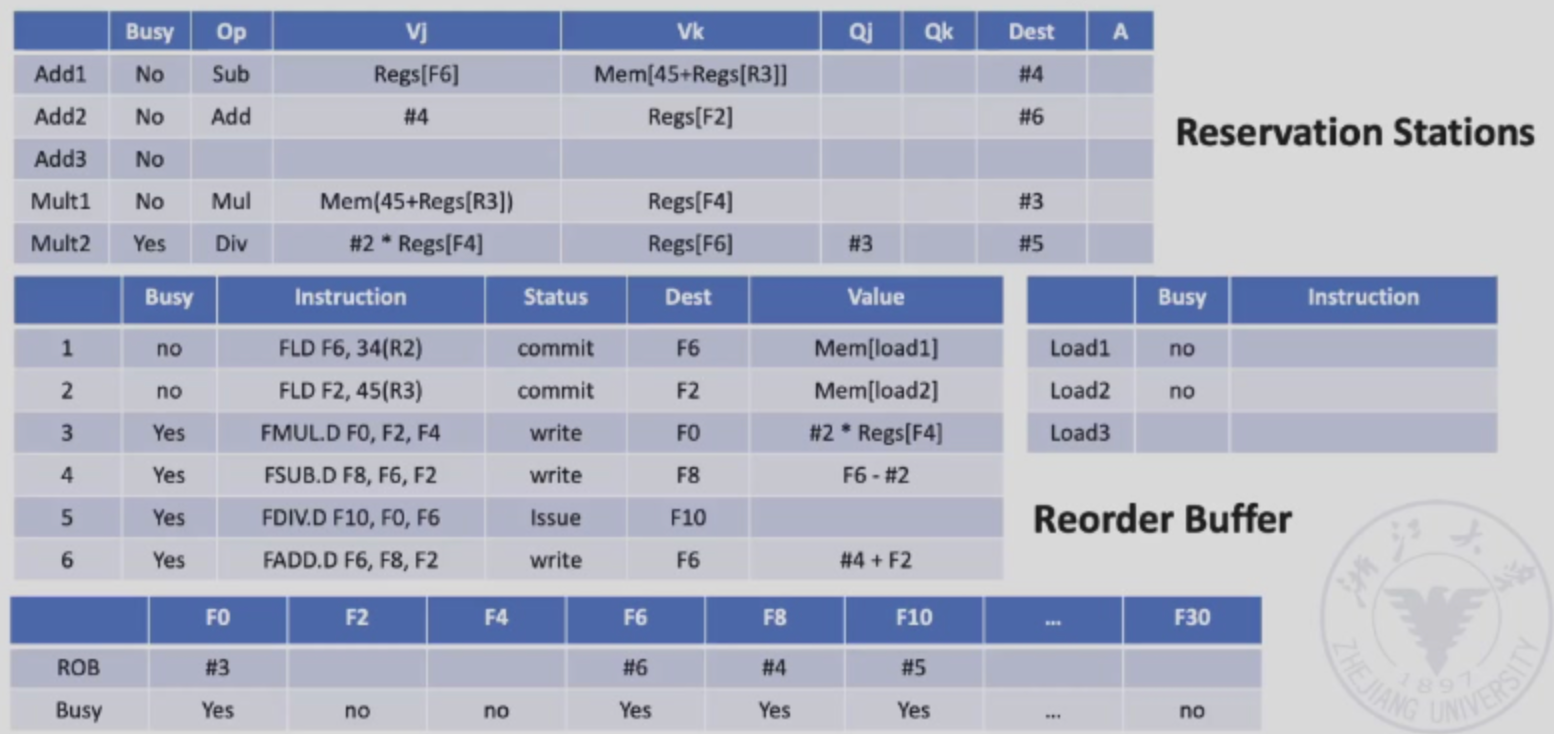

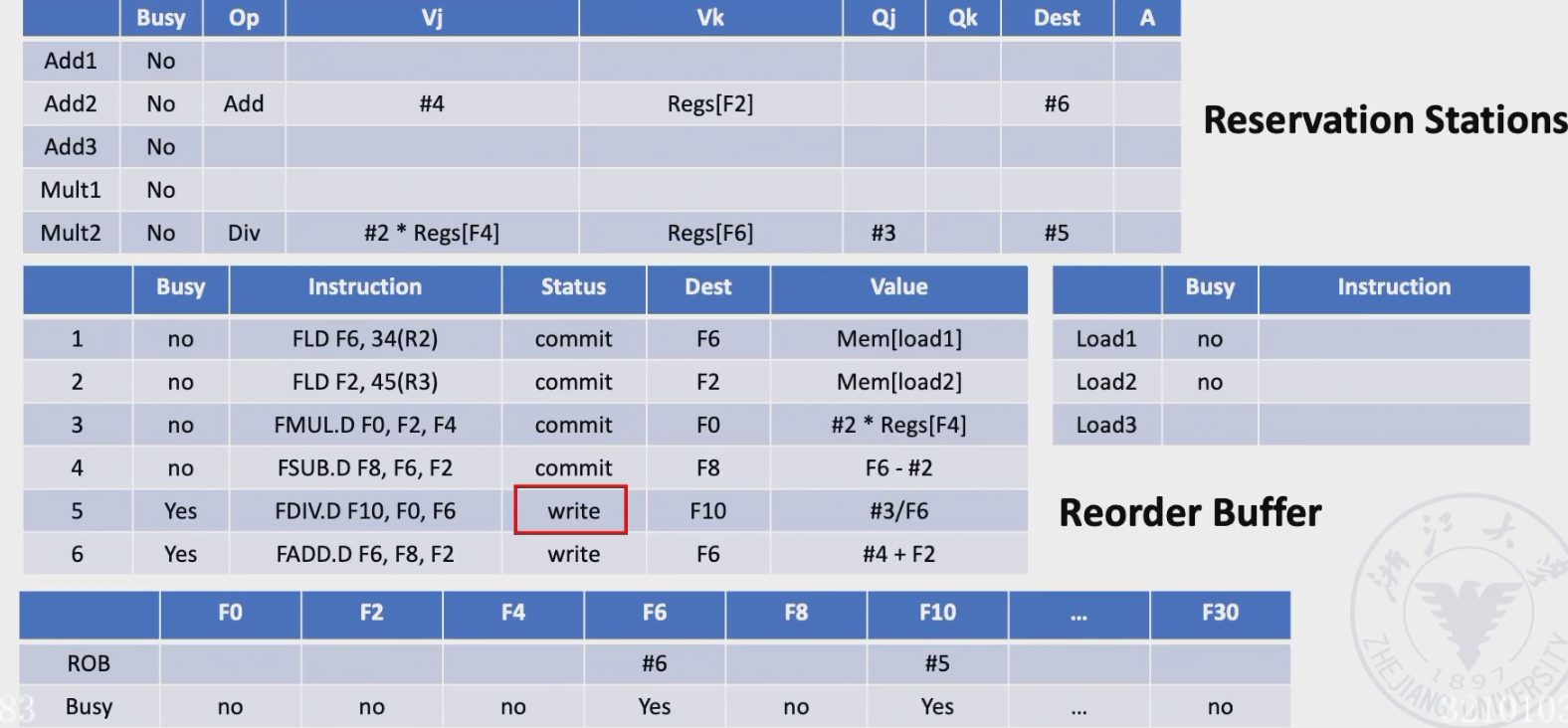

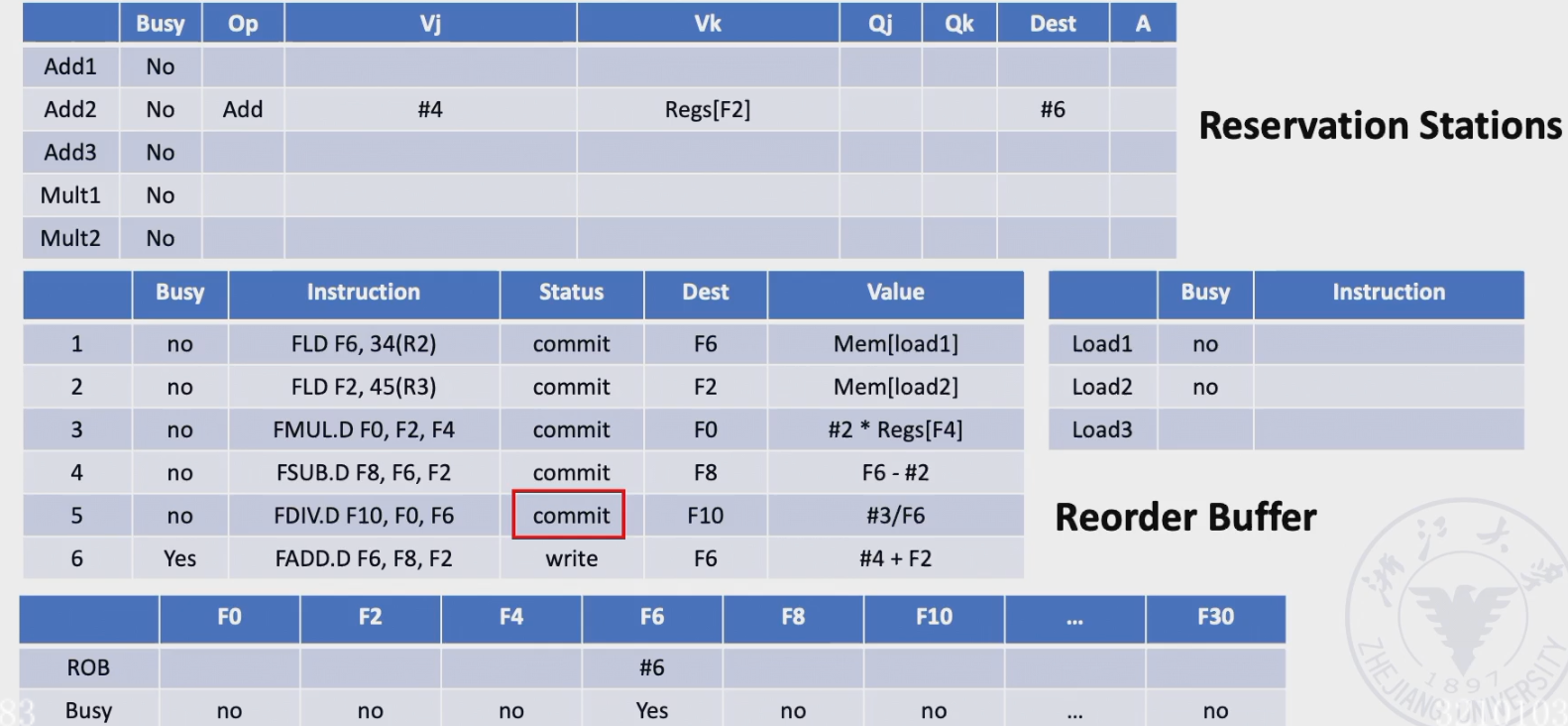

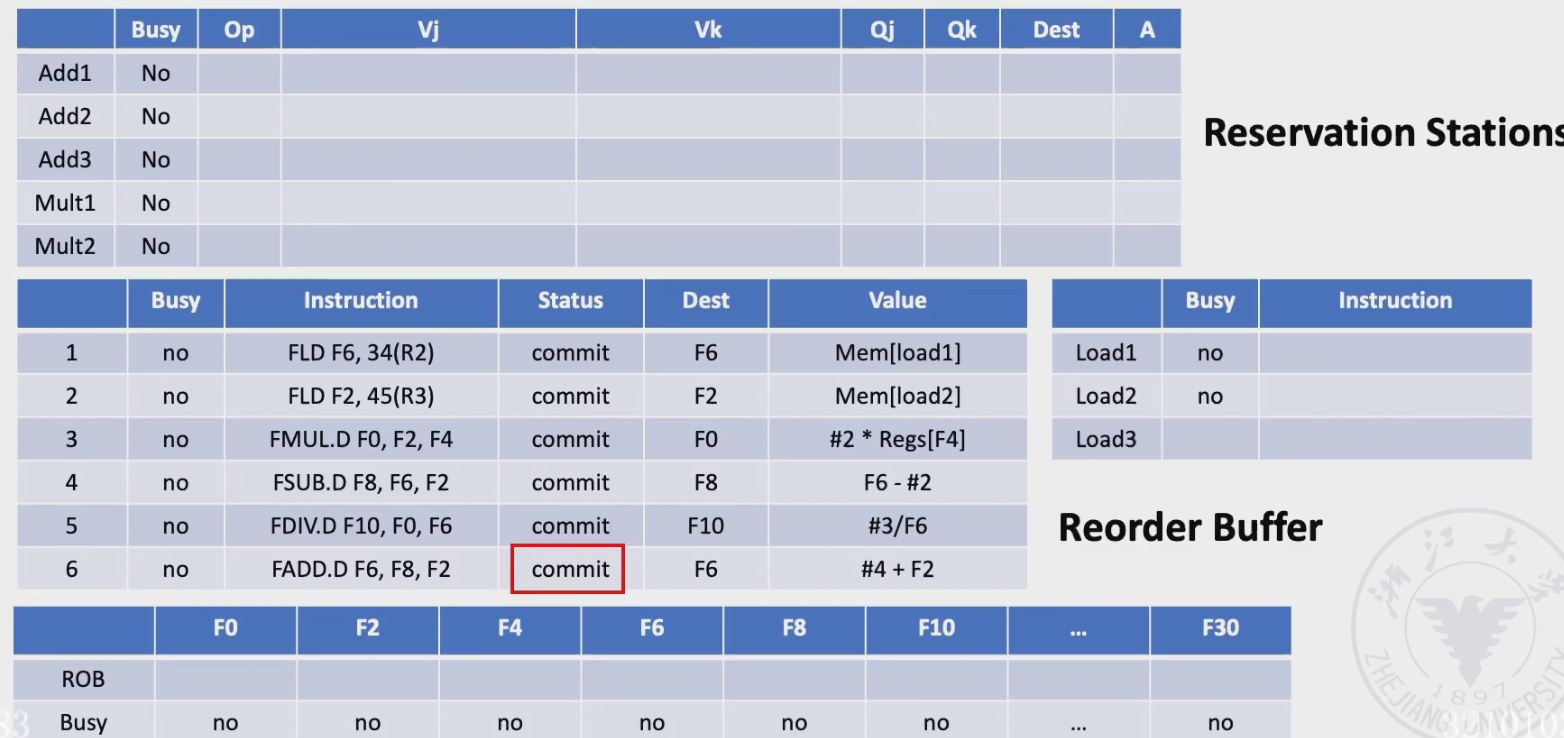

- 保留栈区状态表

- 主要是添加了Dest,用于记录写入的ROB的编号;

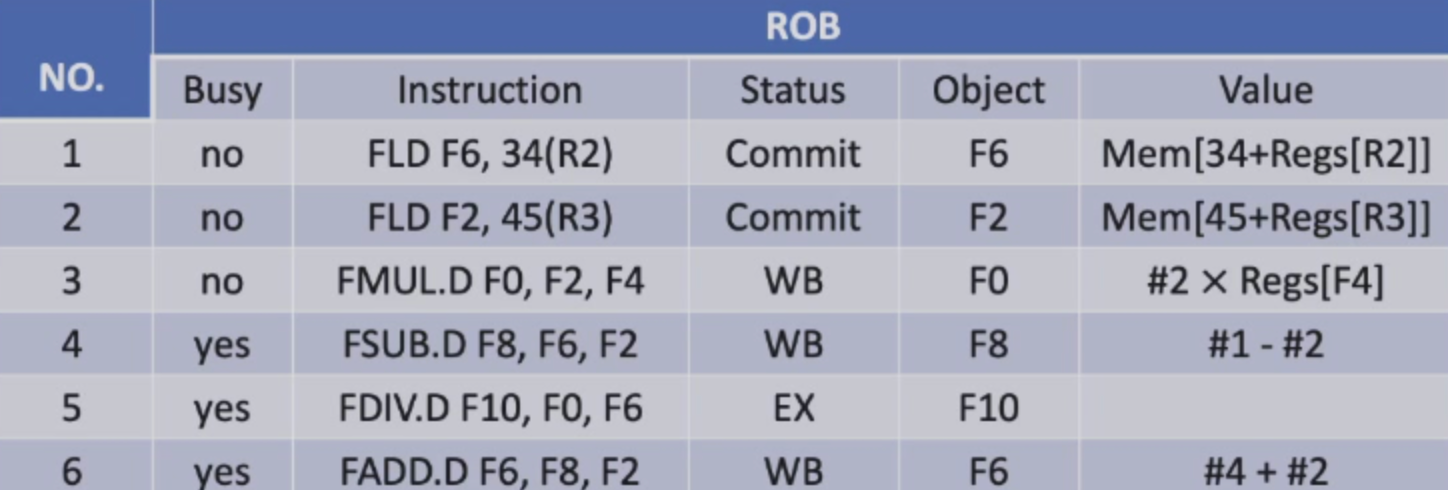

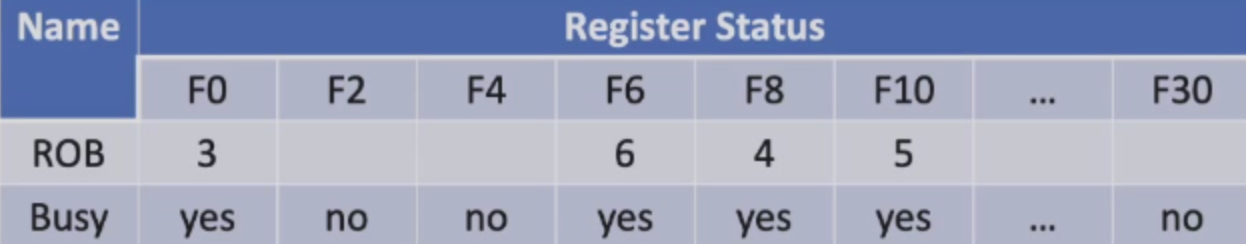

- ROB状态表

- 结果寄存器

- 多了一行ROB和寄存器的对应表,按照编号从小到大提交;

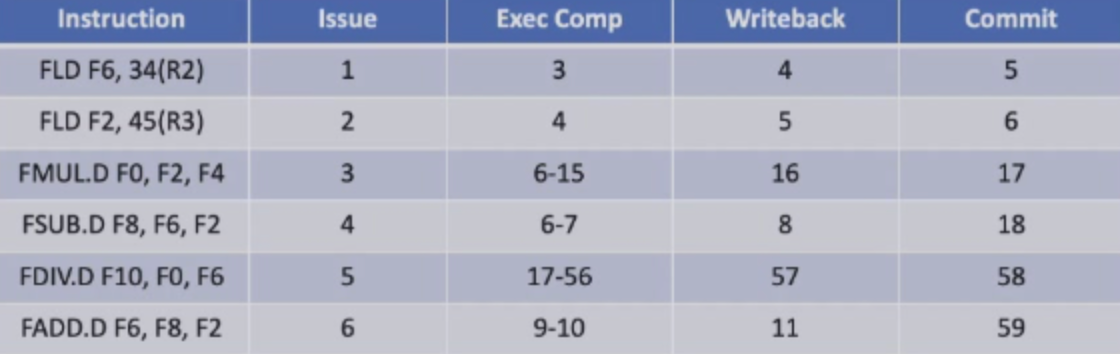

4. 课堂作业¶

- 前面的所有阶段都和托马斯罗算法一模一样,只需要再托马斯罗算法后面再添加一列;

-

-

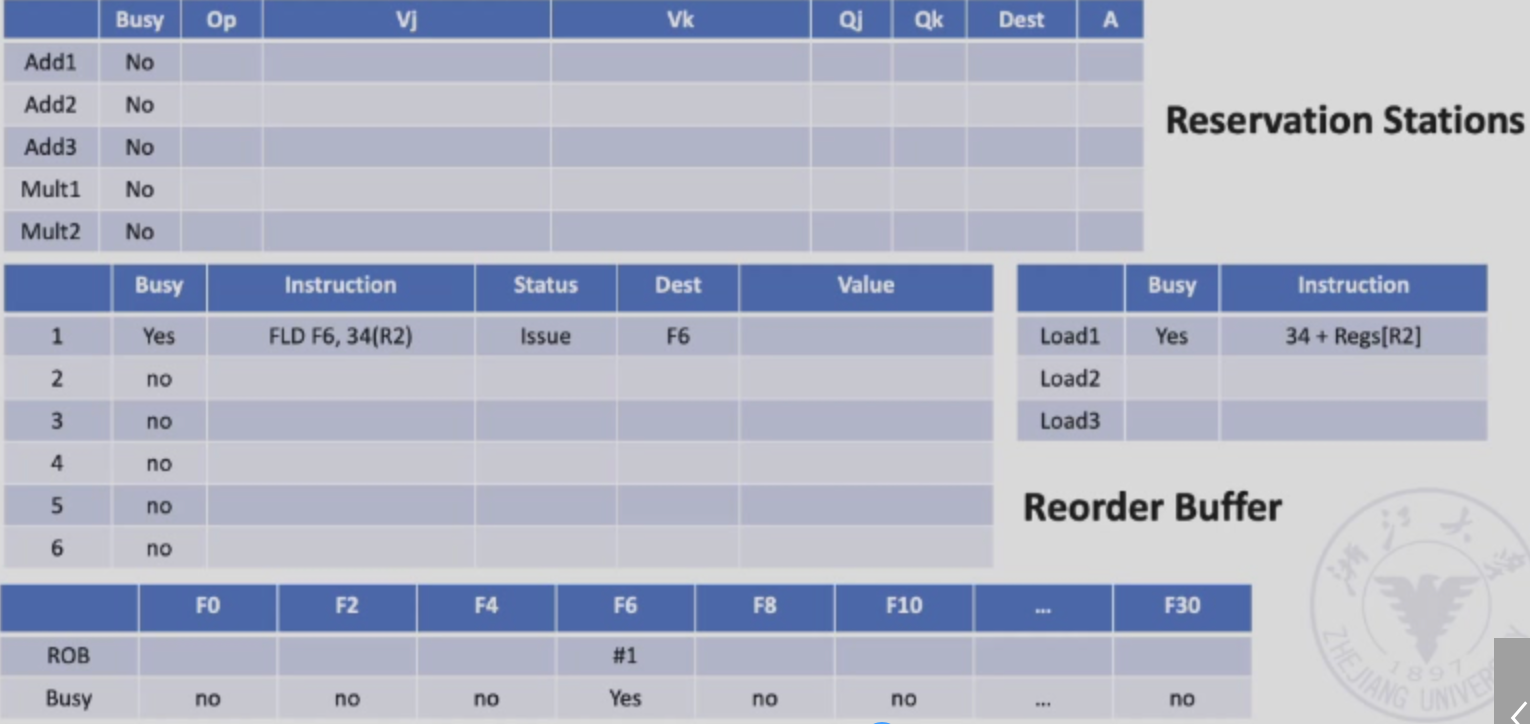

Cycle 1:第一条指令流出

-

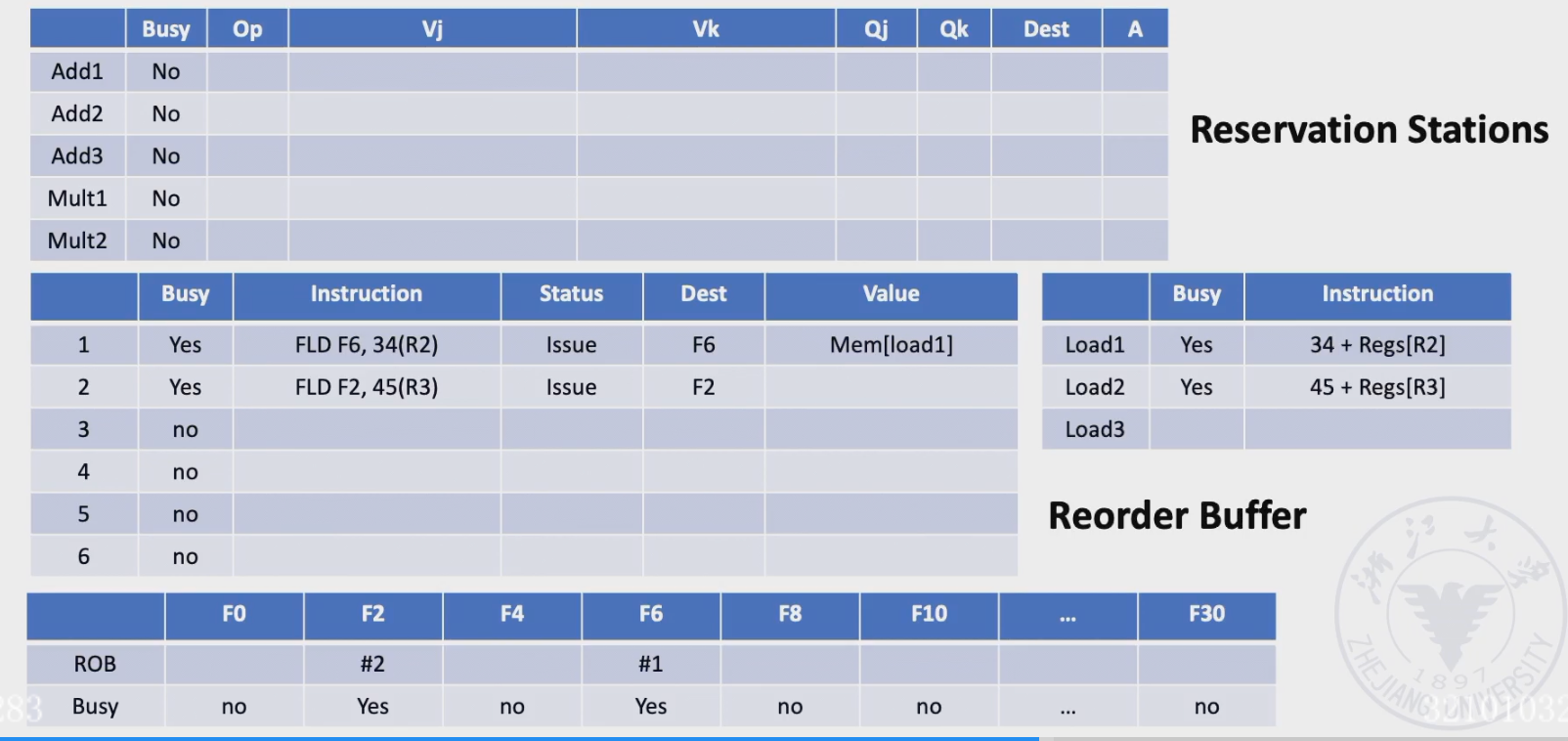

Cycle 2:第一条指令计算地址,第二条指令流出

-

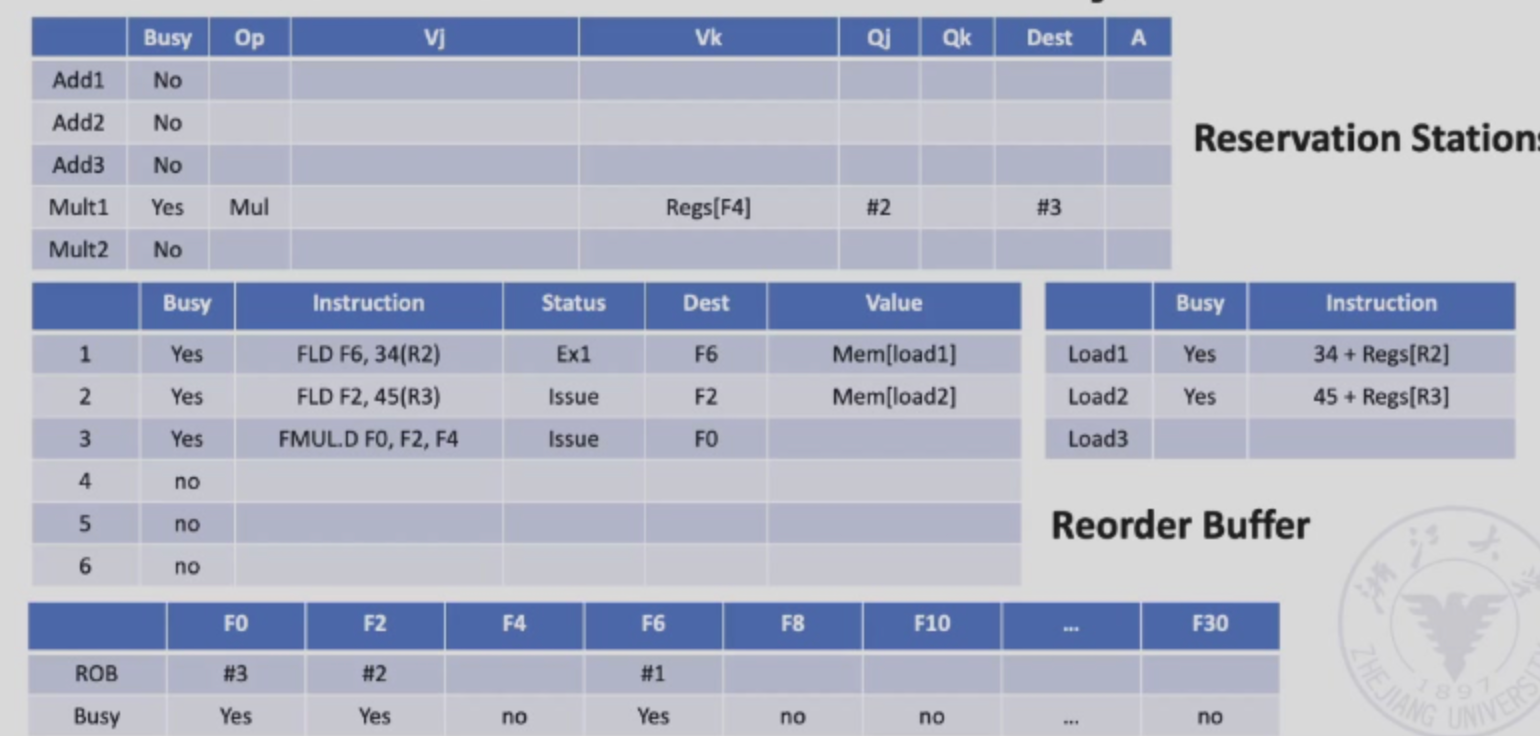

Cycle 3:第一条指令开始执行,第二条指令计算地址,第三条指令流出

-

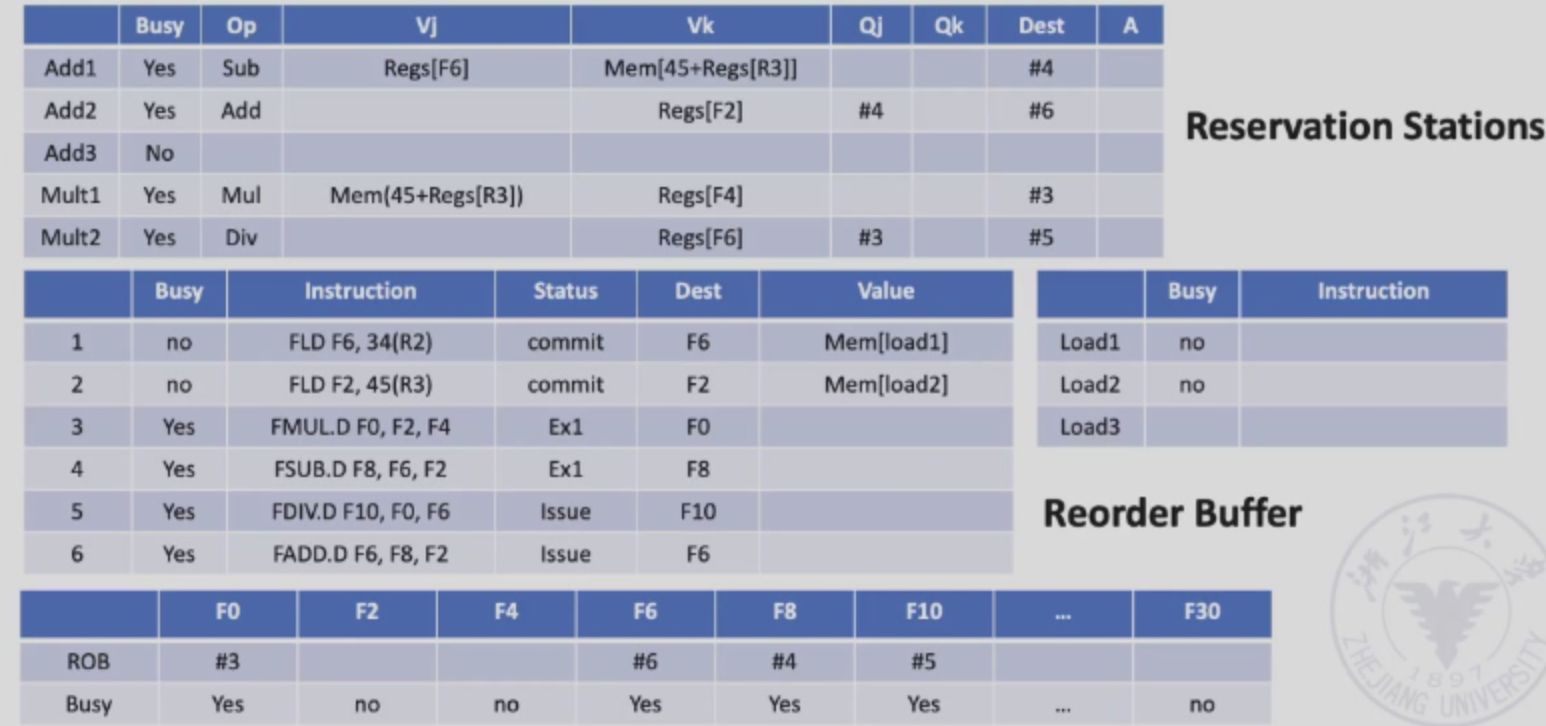

Cycle 4:第三条和第四条指令都要等F2,不能执行

-

Cycle 5:第三条和第四条指令都要等F2,不能执行

-

Cycle 6:第三条和第四条指令开始执行

-

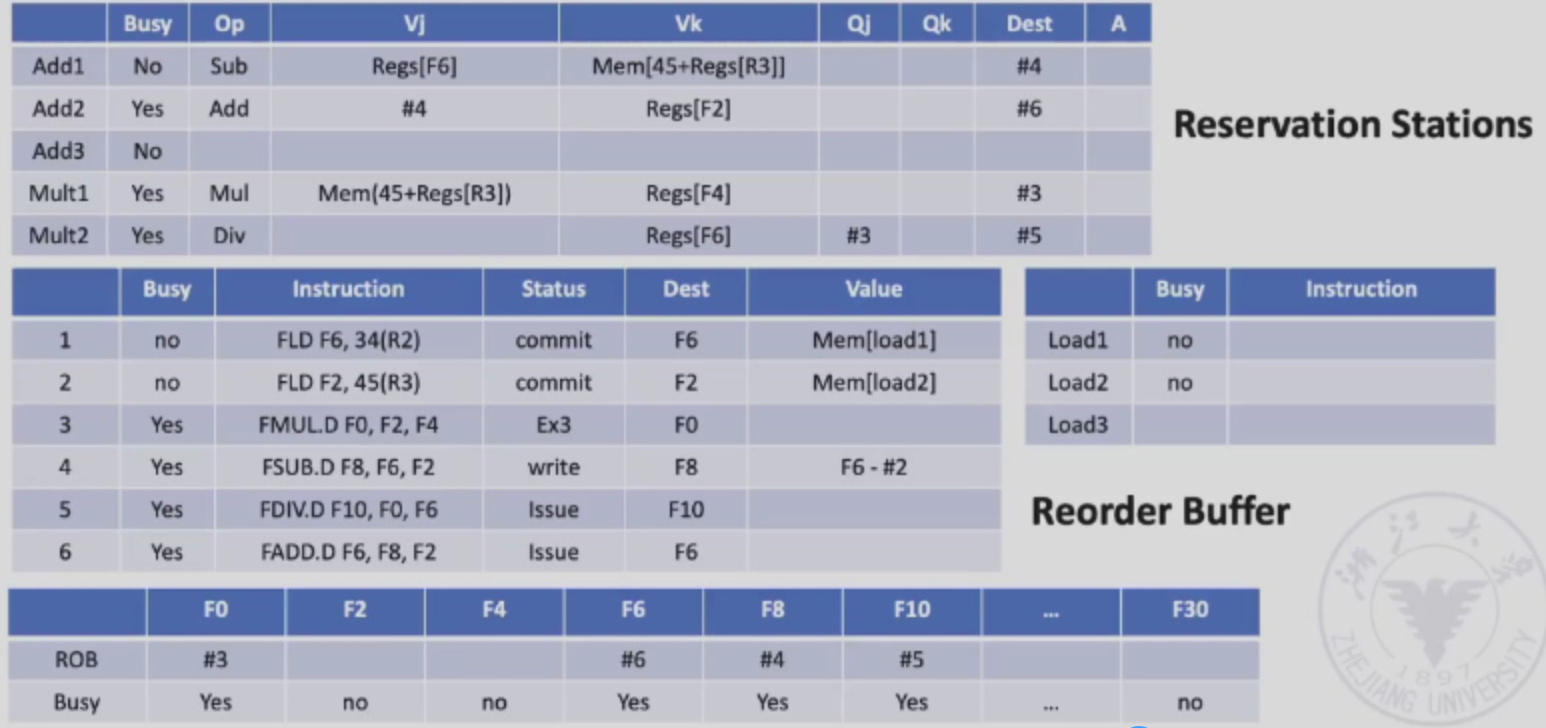

Cycle 8:FSUB写结果

-

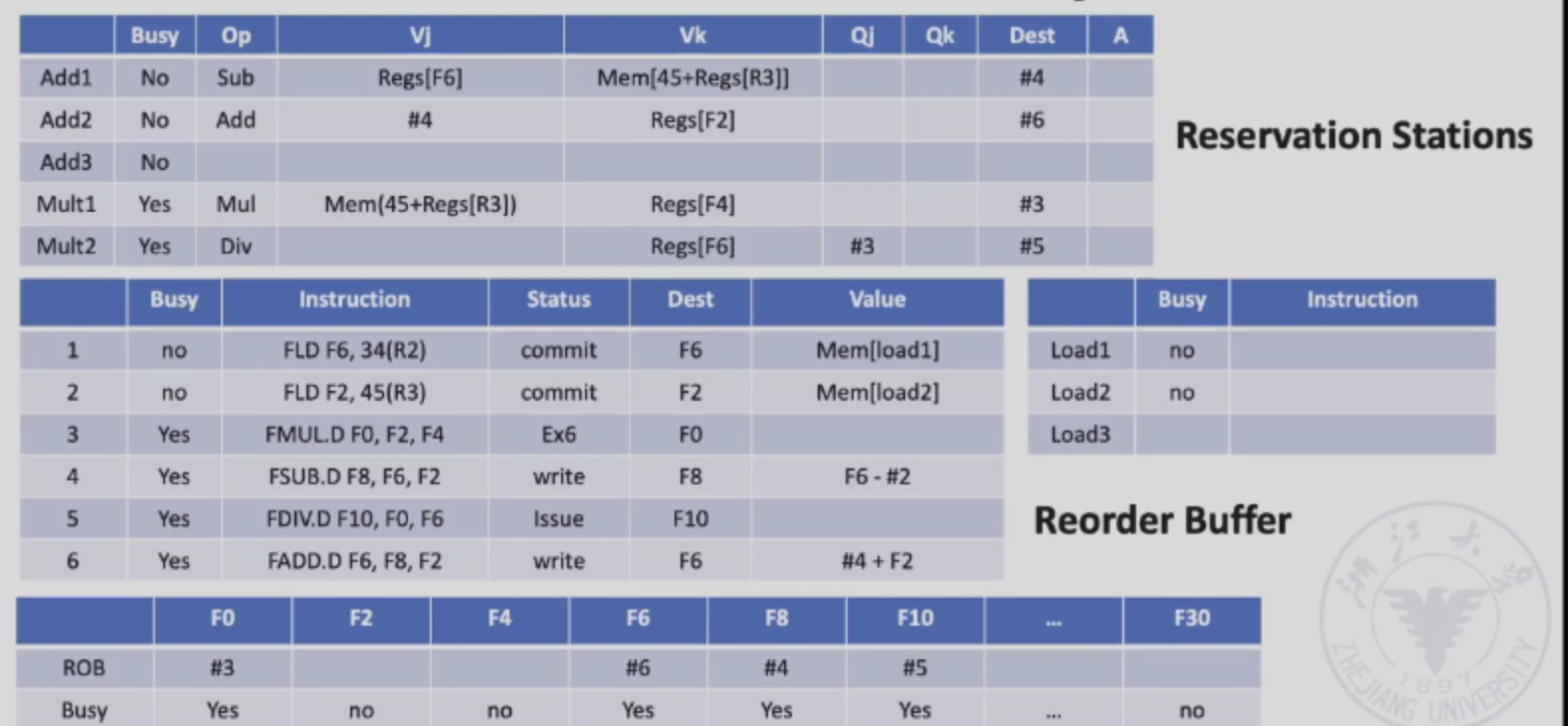

Cycle 11:

-

Cycle 16:

-

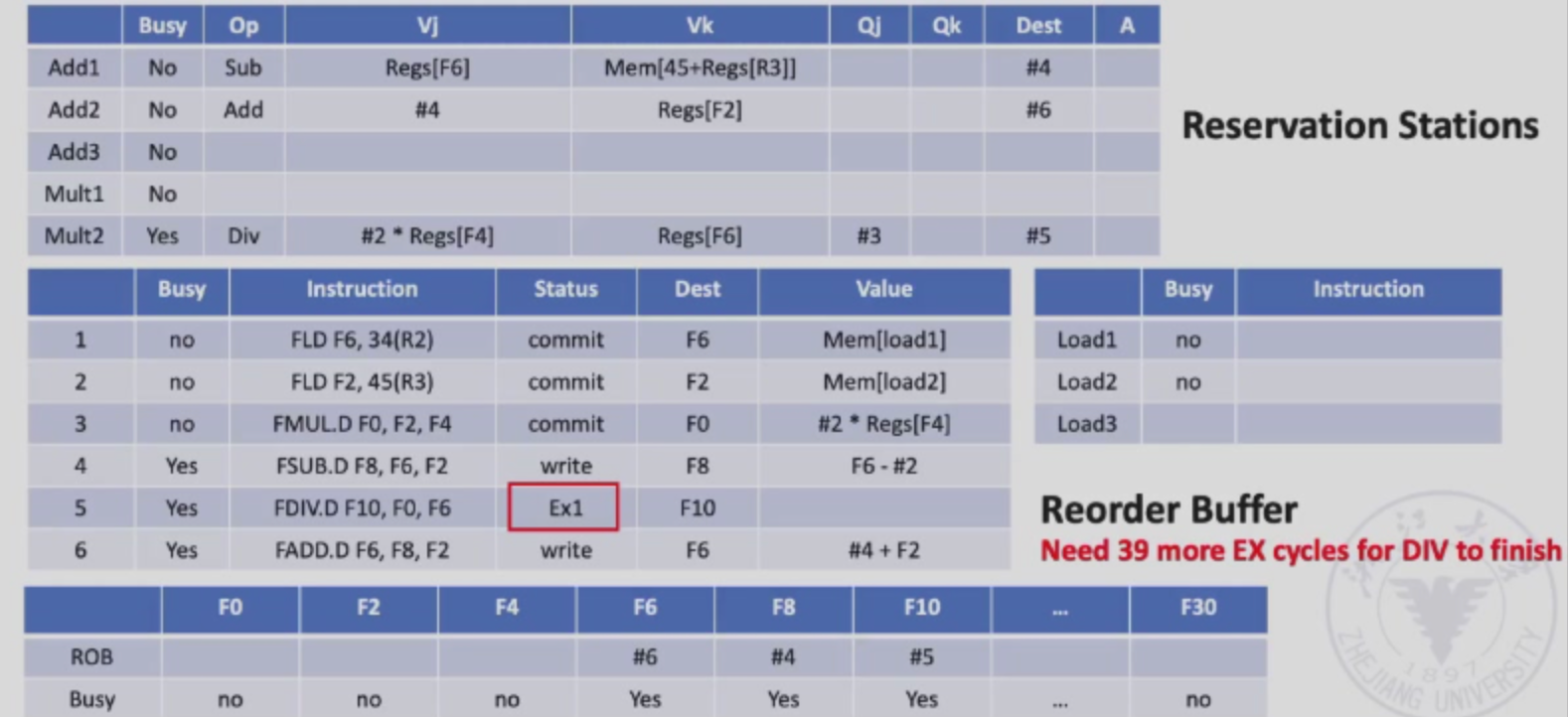

Cycle 17:第三条指令commit,FDIV等到了结果进入了EX段

-

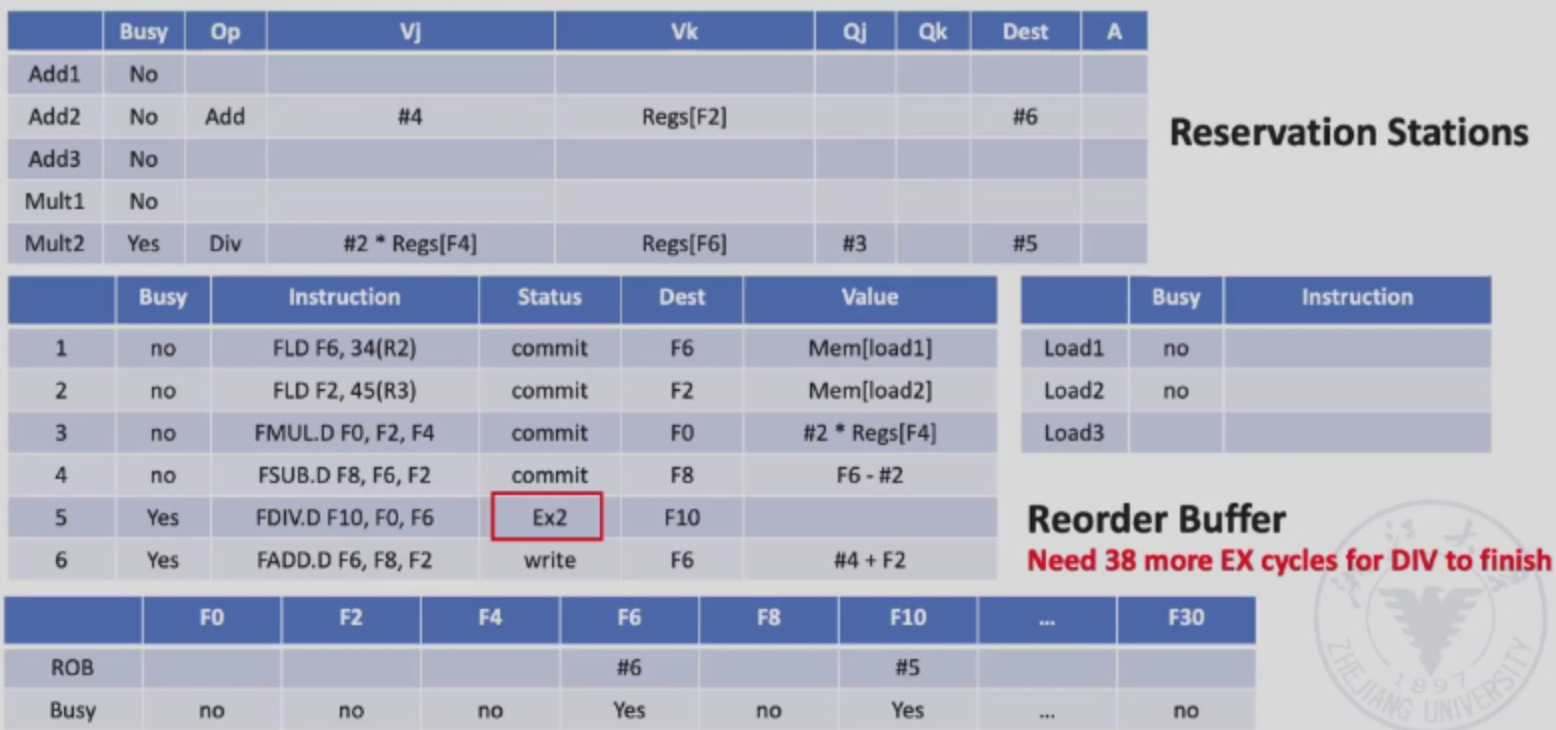

Cycle 18:

-

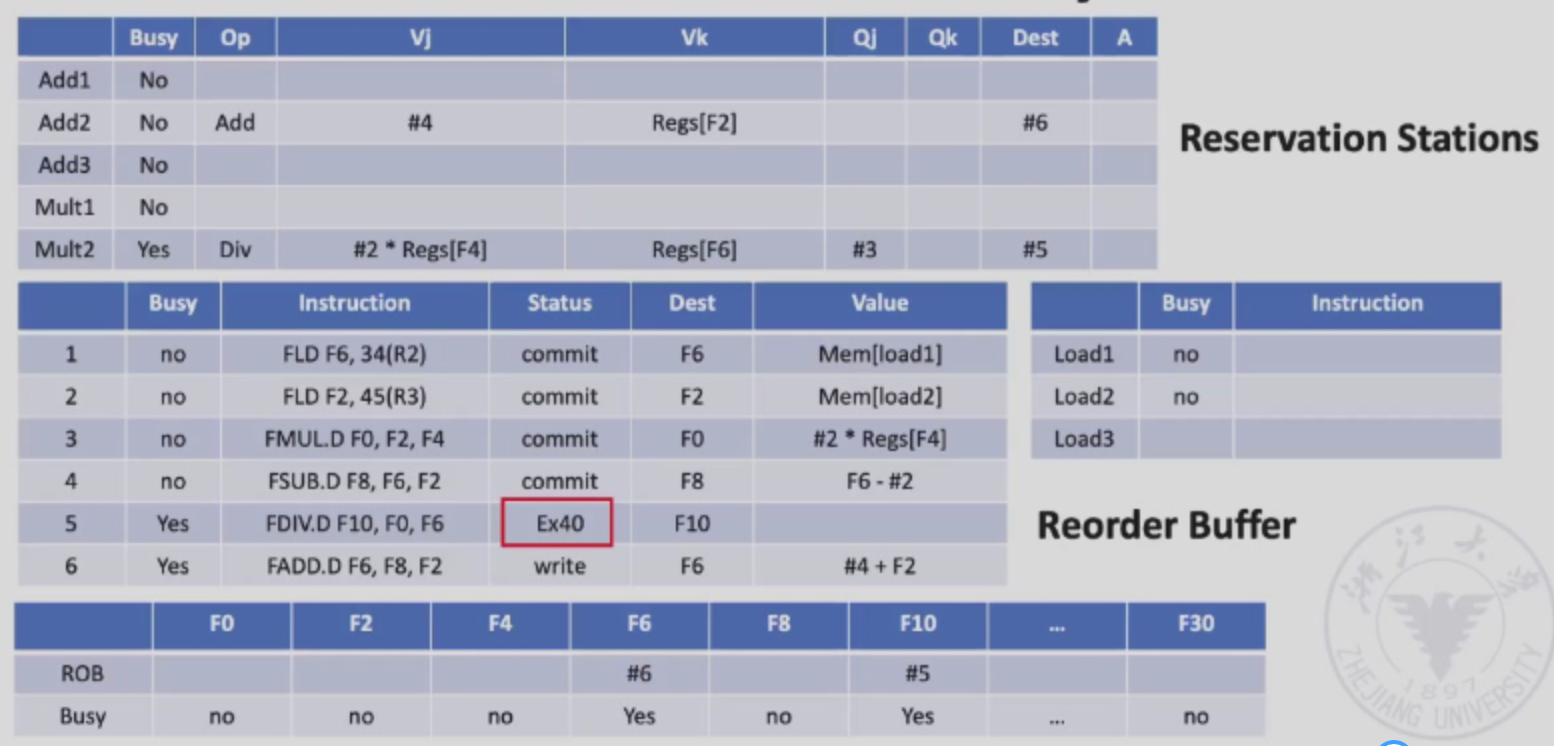

Cycle 56:

-

Cycle 57:

-

Cycle 58:

-

Cycle 59:

-

5. 总结¶

- 执行乱序,提交顺序,可以保证程序能够顺序完成,但是硬件比较复杂;

本文总阅读量次